1. Testbench (테스트벤치)

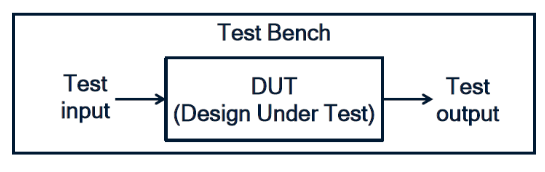

Testbench는 설계된 하드웨어 모듈을 시뮬레이션하고 검증하기 위해 작성된 코드입니다. 실제 하드웨어에서 사용하는 입력 신호를 제공하고, 결과가 예상대로 나오는지 확인하는 역할을 합니다. Testbench는 실제 하드웨어로 구현되지 않으며, 시뮬레이션에서만 동작합니다.

Testbench의 주요 기능:

- 입력 신호 생성: Testbench는 DUT에 필요한 입력 신호를 생성합니다. 이 신호들은 클록, 리셋, 데이터 입력 등 DUT의 동작을 유도하는 모든 신호를 포함합니다.

- 결과 검증: Testbench는 DUT로부터 나오는 출력 신호를 확인하고, 예상한 결과와 비교하여 DUT가 올바르게 동작하는지 검증합니다.

- 시뮬레이션 종료: 특정 시간 후 시뮬레이션을 종료하거나 특정 조건이 충족되면 시뮬레이션을 자동으로 종료합니다.

2. DUT (Device Under Test, 테스트 대상 장치)

DUT는 Testbench에서 검증하려는 실제 설계 모듈입니다. DUT는 최종적으로 하드웨어로 구현되며, Testbench에서 생성된 신호를 받아 그에 따라 동작하는 시스템의 중심이 됩니다.

DUT의 주요 역할:

- 설계된 하드웨어 동작: DUT는 설계자가 구현한 하드웨어의 기능을 수행하는 모듈입니다. Testbench에서 제공된 입력 신호에 따라 동작하며, 출력 신호를 생성합니다.

- 검증 대상: DUT는 검증 대상이므로, Testbench를 통해 올바르게 동작하는지 여부가 테스트됩니다. DUT의 출력이 예상한 결과와 일치하는지 확인하는 것이 Testbench의 목적입니다.

실습) Clock Gating Model 설계하기

> Logic을 사용하지 않을 때에도 Clock신호를 계속 입력하게 된다면 Power을 계속 소모하게 됩니다.

이를 방지 하고자, 전력 절감 기술 중 하나로써, Clock 을 On/Off시키는 Clock Gating Model을 사용합니다.

>실제 현업에서 Clock을 함부로 건들이면 여러 문제가 야기 될 수 있기 때문에, 보통 Clock Gating용 Cell을 Library에서 불러서 사용합니다.

- Verilog Code

* https://github.com/Vamosssss/Basic/tree/main/02.%20Clock_Gating_model

'Verilog HDL > Basics' 카테고리의 다른 글

| 06. Combination Logic (0) | 2024.10.06 |

|---|---|

| 05. D Flip-Flop & Reset(실습) (0) | 2024.10.06 |

| 04. D Flip-Flop (0) | 2024.10.06 |

| 03. Values & Reset (0) | 2024.10.06 |

| 01. Clock 생성하기 (0) | 2024.10.06 |