FPGA(Field-Programmable Gate Array)는 SoC(System on Chip) 설계와 제품 개발에서 다양한 방식으로 활용될 수 있습니다. FPGA는 설계자가 직접 하드웨어 구조를 프로그래밍할 수 있어 유연성과 빠른 개발이 가능하다는 장점이 있습니다. 이를 바탕으로 제품 개발과 SoC 제작에 어떻게 사용될 수 있는지 몇 가지 중요한 활용 방법을 살펴보겠습니다.

1. FPGA의 제품 활용 방안

- 프로토타이핑 및 검증: FPGA는 SoC의 하드웨어 설계를 실제 실리콘으로 구현하기 전에 검증하는 데 중요한 역할을 합니다. SoC 설계의 RTL 코드를 FPGA에 다운로드하여 실시간 테스트를 통해 오류를 조기에 발견할 수 있습니다. 이를 통해 설계 최적화와 실리콘 제작 전 하드웨어 검증을 효과적으로 수행할 수 있습니다.

- 저비용, 소규모 양산 제품: 일부 제품에서는 ASIC(Application-Specific Integrated Circuit)으로 대체하기 전에 소량 생산 제품에 FPGA를 사용하기도 합니다. FPGA는 소량 생산이나 시장 검증 제품에서 비용 효율적이고 유연한 솔루션을 제공합니다.

- 고속 데이터 처리 및 맞춤형 연산: FPGA는 병렬 처리를 통해 고속 연산이 필요한 분야에서 사용될 수 있습니다. 이미지 처리, 신호 처리, 통신 장비 등에서 특정 알고리즘을 하드웨어 가속기로 구현하여 높은 성능을 요구하는 애플리케이션에 적합합니다.

- 업그레이드 가능한 하드웨어 플랫폼: FPGA의 재프로그램 가능성을 이용하여, 하드웨어 수준에서 기능을 추가하거나 성능을 개선할 수 있습니다. 이 방식은 IoT 기기나 통신 장비에서 새로운 프로토콜 지원이나 하드웨어 업그레이드를 용이하게 할 수 있습니다.

2. SoC 설계에서 FPGA의 활용

- 초기 프로토타이핑: SoC 설계 초기 단계에서, FPGA는 시스템 검증과 성능 평가에 중요한 도구입니다. SoC의 하드웨어 설계를 FPGA에서 미리 구현하고, 이를 통해 시스템 통합 테스트를 수행할 수 있습니다. 실제 ASIC이나 SoC가 제작되기 전에 성능과 기능을 확인할 수 있는 효과적인 방법입니다.

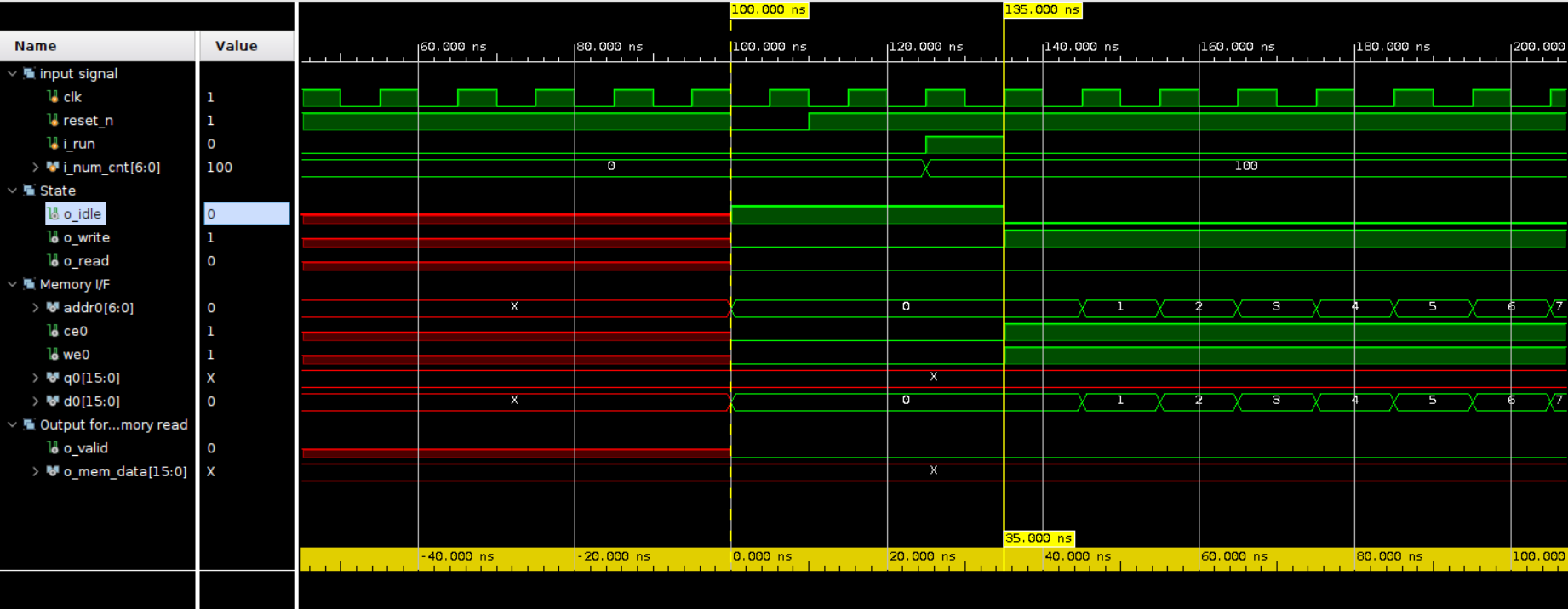

- IP 검증 및 통합: FPGA는 SoC 설계 시 사용되는 IP(Intellectual Property) 블록들을 통합하여 검증하는 과정에서도 활용됩니다. 예를 들어, 메모리 제어기나 통신 프로토콜 IP를 FPGA에 구현하여 소프트웨어와 하드웨어 간 상호작용을 사전에 테스트할 수 있습니다.

- SoC의 가속기 역할: FPGA는 SoC 설계에서 하드웨어 가속기로 활용될 수 있습니다. SoC 내부에서 FPGA를 협력 처리 장치로 사용하여 특정 작업을 가속화하고, SoC의 성능을 극대화하는 데 기여할 수 있습니다. 예를 들어, 머신러닝, 신호 처리, 암호화 연산 등을 FPGA로 구현하여 CPU의 부담을 줄이고 성능을 개선할 수 있습니다.

- 칩 설계 검증 환경: FPGA는 SoC 설계의 시스템 레벨 검증에서도 사용됩니다. SoC 설계에서 각종 인터페이스나 통신 프로토콜을 검증할 때, FPGA를 사용하여 실제 환경에서 동작하는지 확인할 수 있습니다.

'Verilog HDL > FPGA' 카테고리의 다른 글

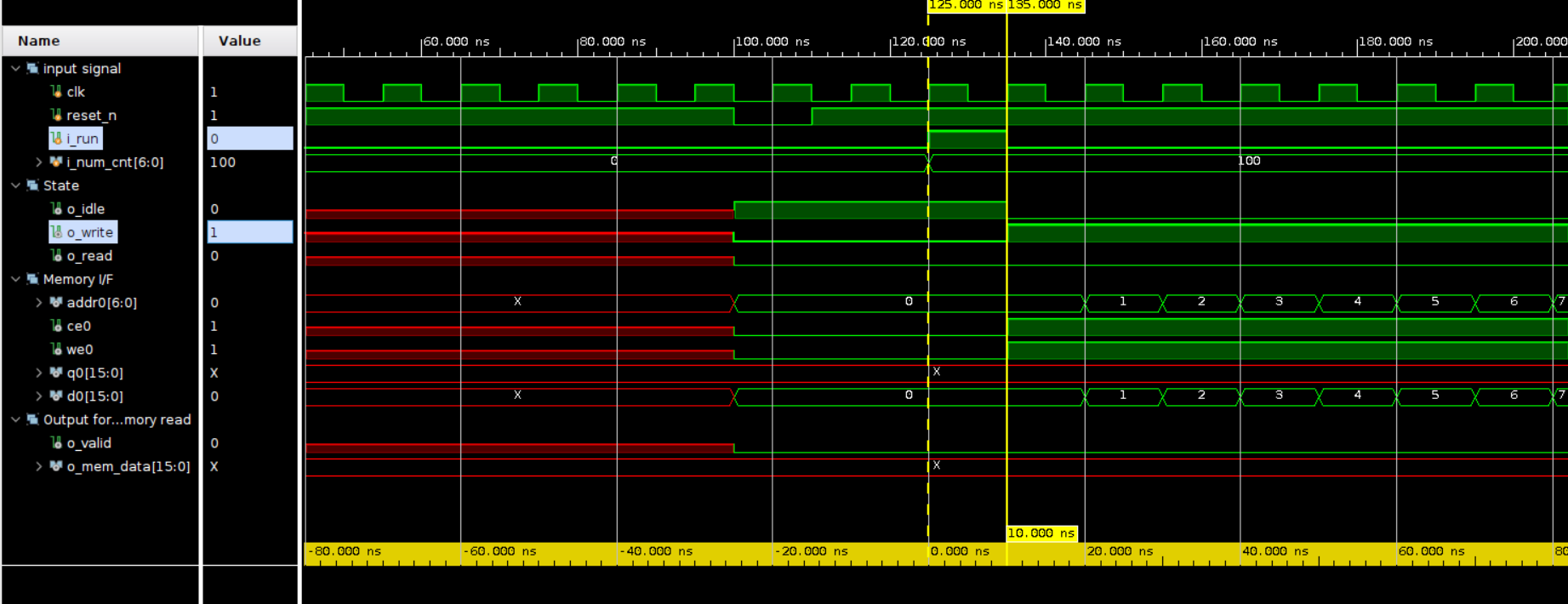

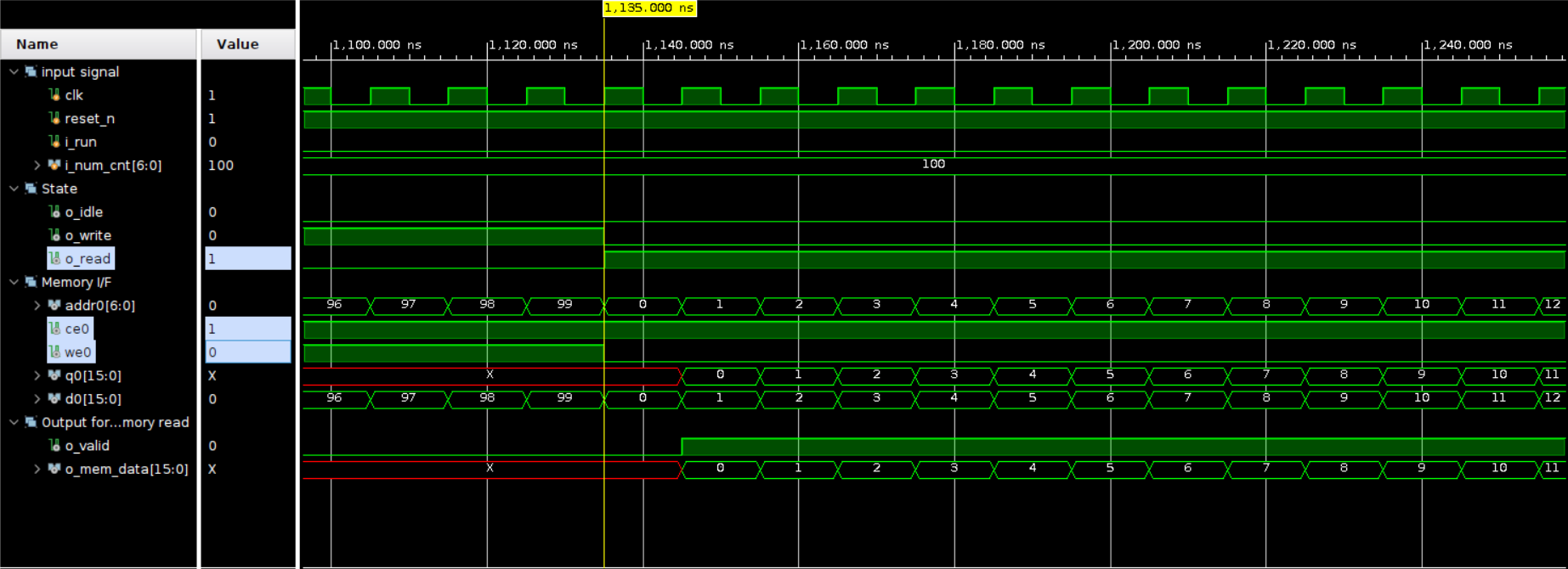

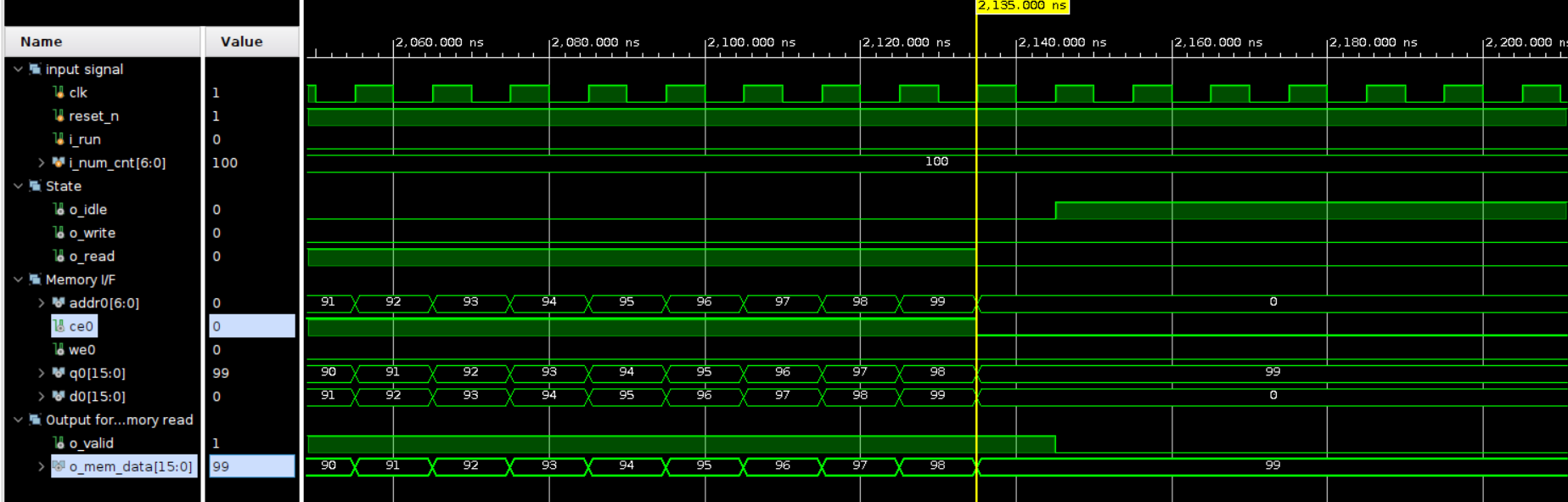

| 02. FPGA BRAM에 Write/Read해보기. (0) | 2024.10.08 |

|---|---|

| 01. FPGA의 BRAM이해하기(SRAM과 같은 동작 방식) (0) | 2024.10.08 |