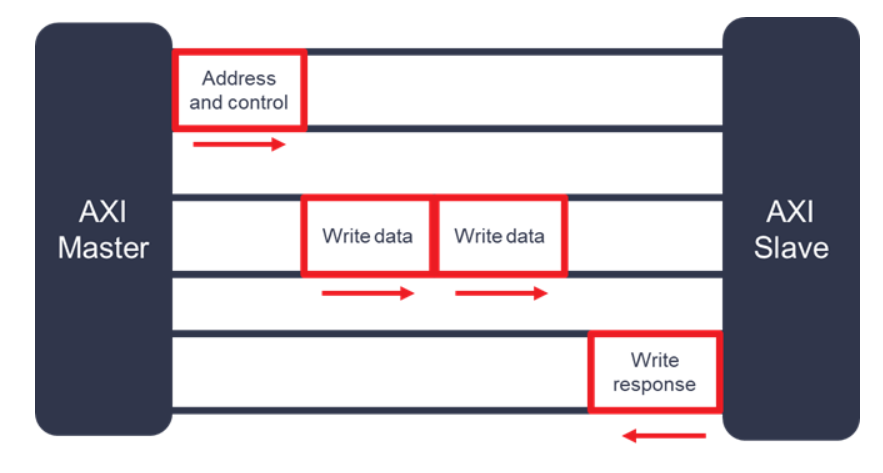

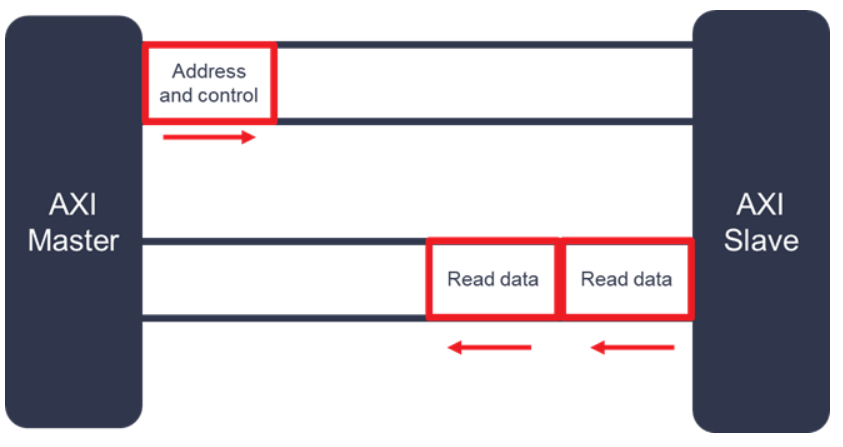

AXI(Advanced eXtensible Interface) 프로토콜에서 **Read Operation(읽기 연산)**은 마스터가 슬레이브로부터 데이터를 읽어오는 과정입니다. 이 과정도 두 가지 주요 단계로 이루어지며, 각각의 단계에서 독립적인 채널을 사용합니다. AXI의 읽기 연산은 파이프라인 방식으로 동작하여 주소 전송과 데이터 전송이 병렬로 처리될 수 있습니다.

AXI Read Operation 단계

- Read Address Phase (읽기 주소 단계)

- Read Data Phase (읽기 데이터 단계)

1. Read Address Phase (읽기 주소 단계)

- 목적: 마스터가 슬레이브에게 읽어올 메모리 주소 및 관련 정보를 전송합니다.

- 채널: Read Address Channel (AR)

동작 순서

- 마스터는 읽고자 하는 메모리의 주소를 ARADDR 신호를 통해 슬레이브로 전송합니다. 이때 읽기 데이터의 길이, 크기 및 버스트 타입 등의 정보를 함께 전달할 수 있습니다.

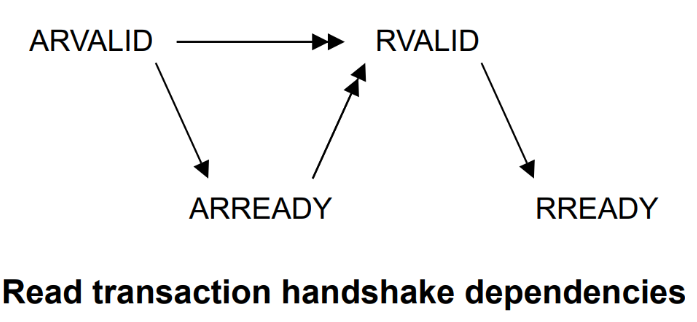

- 마스터는 ARVALID 신호를 활성화하여 주소 정보가 유효하다는 신호를 보냅니다.

- 슬레이브가 주소 정보를 받을 준비가 되면 ARREADY 신호를 활성화하여 수신 준비가 되었음을 마스터에게 알립니다.

- 주소 전송이 완료되면, 슬레이브는 해당 주소의 데이터를 준비하기 시작합니다.

주요 신호

- ARADDR: 읽고자 하는 메모리의 주소.

- ARLEN: 버스트 전송 시 전송할 데이터의 길이.

- ARSIZE: 전송할 데이터의 크기 (예: 8비트, 16비트 등).

- ARBURST: 버스트 모드일 때, 버스트 타입을 지정.

- ARVALID: 읽기 주소가 유효함을 나타내는 신호.

- ARREADY: 슬레이브가 읽기 주소를 받을 준비가 되었음을 나타내는 신호.

2. Read Data Phase (읽기 데이터 단계)

- 목적: 슬레이브가 해당 메모리 주소에서 데이터를 준비하여 마스터에게 전달합니다.

- 채널: Read Data Channel (R)

동작 순서

- 슬레이브는 읽기 주소를 수신한 후 해당 주소의 데이터를 준비하여 RDATA 신호를 통해 마스터에게 전송합니다.

- 슬레이브는 RVALID 신호를 활성화하여 데이터가 유효함을 나타냅니다.

- 마스터는 RREADY 신호를 활성화하여 데이터를 받을 준비가 되었음을 알립니다.

- 슬레이브는 버스트 모드로 여러 데이터를 전송할 수 있으며, RLAST 신호를 통해 버스트 전송의 마지막 데이터를 나타냅니다.

- RRESP 신호는 데이터 전송의 성공 여부나 오류 여부를 나타냅니다.

주요 신호

- RDATA: 마스터에게 전송할 실제 읽기 데이터.

- RRESP: 데이터 전송이 성공했는지, 오류가 있었는지 나타내는 응답 신호.

- RVALID: 읽기 데이터가 유효함을 나타내는 신호.

- RREADY: 마스터가 데이터를 받을 준비가 되었음을 나타내는 신호.

- RLAST: 버스트 전송일 때 마지막 데이터를 나타내는 신호.

AXI Read Operation의 병렬성

AXI 프로토콜에서 읽기 주소 전송과 읽기 데이터 전송이 병렬로 처리될 수 있습니다. 즉, 마스터는 여러 번의 읽기 요청을 동시에 보내고, 슬레이브는 각 요청에 대해 데이터를 차례로 전송할 수 있습니다. 또한, 읽기 작업은 비동기적으로 동작하므로, 마스터는 슬레이브로부터 응답을 기다리는 동안 다른 작업을 진행할 수 있습니다.

AXI Read Operation의 예시

- 주소 전송:

- 마스터가 슬레이브에게 메모리 주소 ARADDR = 0x1000에서 데이터를 읽어오라고 요청합니다.

- 마스터는 ARVALID 신호를 활성화하여 슬레이브에게 주소가 유효함을 알립니다.

- 슬레이브는 ARREADY 신호를 활성화하여 읽기 주소를 수신할 준비가 되었음을 마스터에게 알립니다.

- 데이터 전송:

- 슬레이브는 해당 주소의 데이터를 읽어 준비한 후 RDATA 신호로 데이터를 마스터에게 전송합니다.

- 슬레이브는 RVALID 신호를 활성화하여 데이터가 유효함을 나타냅니다.

- 마스터는 RREADY 신호를 통해 데이터를 받을 준비가 되었음을 알립니다.

- 만약 버스트 모드로 여러 데이터를 연속적으로 전송하는 경우, 슬레이브는 RLAST 신호를 통해 마지막 데이터를 전송했음을 알립니다.

AXI Read Operation의 효율성

- 파이프라인 동작: 읽기 주소 단계와 읽기 데이터 단계가 독립적으로 동작하기 때문에, 마스터는 여러 주소를 슬레이브에 보낸 후 동시에 데이터를 받을 수 있습니다.

- 병렬성: 읽기 작업 중 마스터는 다른 읽기 또는 쓰기 작업을 동시에 처리할 수 있습니다.

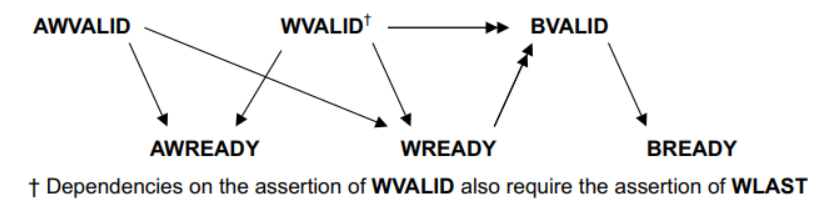

- 핸드셰이킹: 각 단계는 Valid와 Ready 신호를 통해 서로 간의 준비 상태를 확인하므로, 데이터 전송의 정확성과 효율성을 높입니다.

주요 특징 요약

- 주소 전송과 데이터 전송은 독립적으로 이루어지며, 두 단계는 동시에 처리될 수 있어 성능이 향상됩니다.

- Valid-Ready 핸드셰이킹을 통해 마스터와 슬레이브는 각자의 상태에 따라 유연하게 동작할 수 있습니다.

- RRESP 신호를 통해 읽기 작업의 성공 여부를 확인할 수 있으며, 오류 처리가 가능합니다.

결론

AXI의 **읽기 연산(Read Operation)**은 마스터가 슬레이브로부터 데이터를 읽어오는 과정으로, 주소 전송과 데이터 전송이 독립적으로 처리됩니다. 읽기 주소와 데이터 전송은 병렬로 수행되며, 이로 인해 전체 시스템의 성능이 크게 향상됩니다.

* https://adaptivesupport.amd.com/s/article/1053914?language=en_US

'SoC Protocol > AMBA' 카테고리의 다른 글

| 12. AXI Write Operation (0) | 2024.09.27 |

|---|---|

| 11. AXI Interface (0) | 2024.09.27 |

| 10. AXI Channel Dependencies (0) | 2024.09.27 |

| 09. AXI Channel (0) | 2024.09.27 |

| 08. AHB (HTRANS, HSIZE, HBURST) (0) | 2024.09.27 |