Counter

Counter Logic은 디지털 회로에서 특정 이벤트의 발생 횟수를 세기 위해 사용되는 순차 회로입니다. 카운터는 입력 신호에 따라 증가하거나 감소하는 값을 유지하며, 보통 클럭 신호에 동기화되어 동작합니다.

Counter의 동작 원리

- 카운터는 보통 D 플립플롭(D Flip-Flop)을 사용하여 구현됩니다. 클럭 신호가 들어오면 플립플롭의 출력 상태가 변하고, 이 상태가 다음 카운트 값으로 이어집니다.

- 상태 변화는 다음과 같은 논리식을 통해 제어됩니다:

- 업 카운터: Qn+1 = Qn + 1

- 다운 카운터: Qn+1 = Qn - 1

> Counter Logic을 설계할 수 있는 능력을 기르게 된다면 간단하게 LED점등 부터, 현업에서 쓰이는 Memory의 원하는 Address data를 Read/Write하는 메모리 컨트롤러까지 여러 방면으로 사용 할 수 있습니다

또한, Clock, Reset, Sequential Logic, Combinational Logic, OverFlow등 여러 설계 스킬을 사용 할 수 있는 기본이 되는 Logic입니다.

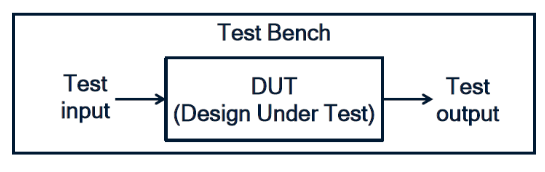

실습) Positive Edge마다 1씩 증가하는 Counter 설계

- Count 100

- Count 100(always) >99

* Essential Clk, Reset

- Verilog Code

* https://github.com/Vamosssss/Basic/tree/main/05.%20Counter

'Verilog HDL > Basics' 카테고리의 다른 글

| 09. FSM (Finite State Machine) (2) | 2024.10.06 |

|---|---|

| 08. Pipeline (1) | 2024.10.06 |

| 06. Combination Logic (0) | 2024.10.06 |

| 05. D Flip-Flop & Reset(실습) (0) | 2024.10.06 |

| 04. D Flip-Flop (0) | 2024.10.06 |