한 데이터 처리 단계의 출력이 다음 단계의 입력으로 이어지는 형태로 연결된 구조를 가리킨다. 이렇게 연결된 데이터 처리 단계는 한 여러 단계가 서로 동시에, 또는 병렬적으로 수행될 수 있어 효율성의 향상을 꾀할 수 있다. 각 단계 사이의 입출력을 중계하기 위해 Buffer가 사용될 수 있다.

Pipeline은 여러 작업 단계를 동시에 처리하여 성능을 향상시키는 기법입니다.

- 레이턴시 (Latency): 작업이 완료되기까지 걸리는 시간으로, 초기에는 길지만 파이프라인이 가동되면 각 클럭 사이클마다 새로운 작업이 완료되어 상대적으로 낮아집니다.

- 처리량 (Throughput): 일정 시간 동안 처리할 수 있는 작업의 양으로, 파이프라인 구조로 인해 작업 흐름이 원활해져 증가합니다.

Hw에서의 Pipeline의 장점

- 성능 향상: 여러 작업을 동시에 처리함으로써 CPU의 자원을 효율적으로 활용하여 전체 성능을 크게 향상시킵니다.

- 자원 활용 극대화: 각 단계가 독립적으로 작동하여 동일한 하드웨어 자원을 더 효과적으로 사용할 수 있습니다. 이를 통해 성능 향상 및 비용 절감이 가능합니다.

- 작업 병렬 처리: 여러 명령어를 동시에 실행할 수 있어 CPU의 처리 능력을 극대화하고, Latency를 줄입니다.

- Throughput 증가: 파이프라인이 완전히 가동되면 매 클럭 사이클마다 작업이 완료되므로, 시스템의 전반적인 처리량이 증가합니다.

> 이러한 이유로 CPU혹은 GPU등의 Architecture 에서 Pipeline을 많이 사용합니다.

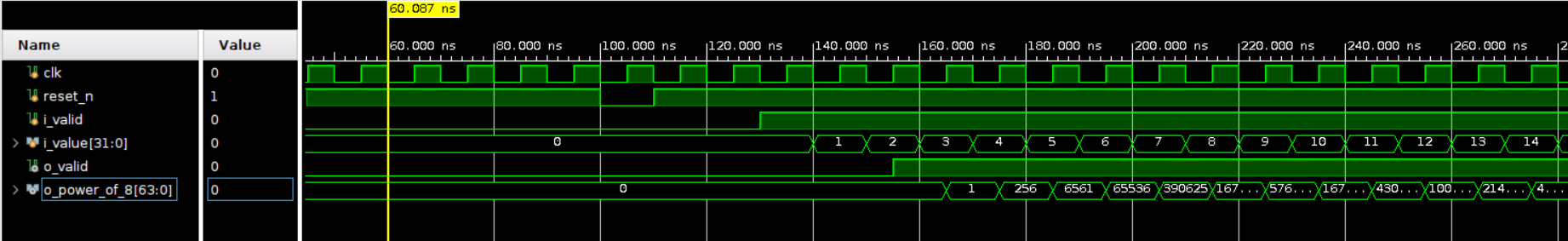

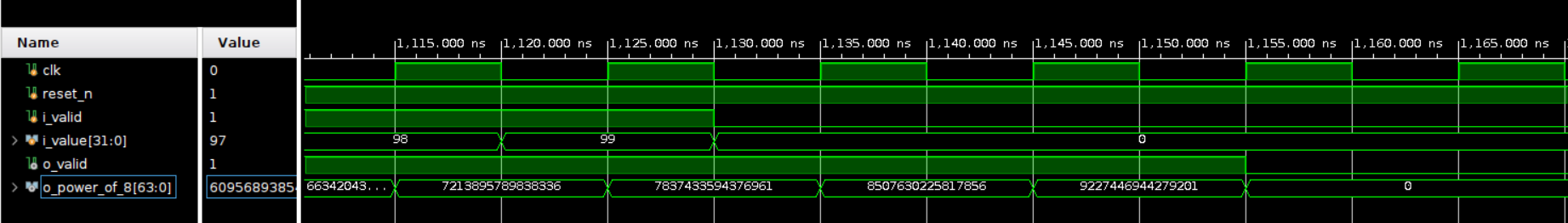

실습) Power of 8 Operation

- Latency : 3 Cycle

- Throughput : 1 Cycle

- Verilog Code

* https://github.com/Vamosssss/Basic/tree/main/06.Pipeline

> SW는 Sequential하기 때문에 Loop가 끝나기 전까지 새로운 입력을 받아서 계산이 불가능합니다.

반면, HW에서는 F/F이라는 Buffer가 있기 때문에 매 Cycle마다 새로운 입력을 받아서 계산이 가능합니다.

예를 들어, HW의 clock이 1GHz라고 한다면, 100번 연산을 하는데 102Cycle이 필요합니다

그에 반해, SW에서는 CPU가 3GHz 라고 하고, 3Cycle마다 결과가 나온다 하더라고 300Cycle이 필요하게 됩니다.

그래서 AI처럼 단순하면서도 많은 연산을 필요로 할 땐 HW를 사용할 수 밖에 없습니다.

그리고, Pipeline을 잘 유지하도록 설계가 되어야 Performance를 잘 끌어 올릴 수 있습니다.

'Verilog HDL > Basics' 카테고리의 다른 글

| 09-1 . FSM(Finite State Machine) Coding Style (0) | 2024.10.07 |

|---|---|

| 09. FSM (Finite State Machine) (2) | 2024.10.06 |

| 07. Counter (0) | 2024.10.06 |

| 06. Combination Logic (0) | 2024.10.06 |

| 05. D Flip-Flop & Reset(실습) (0) | 2024.10.06 |