FSM(Finite State Machine, 유한 상태 기계)은 시스템이 일정한 개수의 상태를 가지며, 현재 상태와 입력 신호에 따라 상태가 변화하고, 그에 따라 출력을 결정하는 논리 구조를 말합니다. FSM은 주로 디지털 시스템 설계에서 사용되며, 복잡한 동작을 간단하게 설계하고 분석할 수 있도록 합니다.

> FSM을 사용하면 비교적 쉽게 Controller를 설계 할 수 있습니다.

참고로 FSM을 사용하지 않고 if else 분기문을 통하여 간단한 control 설계는 가능하지만, HW는 동시성의 개념 때문에 if else 문을 많이 사용하게되면 control이 꼬이게 될 수 있다.

한 번에 오로지 하나의 상태만을 가지게 되며, 현재 상태(Current State)란 임의의 주어진 시간의 상태를 칭한다.

이러한 기계는 어떠한 사건(Event)에 의해 한 상태에서 다른상태로 변화할 수 있으며, 이를 전이(Transition)이라한다.

IDLE >> (i_run==1) >> RUN >> (is_done?) >> DONE >> IDLE

위와 같은 FSM Logic이 있다면 State는 IDEL, RUN, DONE 이렇게 세개가 존재합니다.

현재 상태가 IDLE이고 (i_run==1)일때 RUN State로 전이(Transition)되고, 여기서 (i_run==1)이 Event가 됩니다.

Mealy & Moore Machine

- Moore FSM: 출력이 현재 상태에만 의존하는 구조입니다. 즉, 현재 어떤 상태인지에 따라 출력이 결정됩니다.

- Mealy FSM: 출력이 현재 상태와 입력 신호에 모두 의존하는 구조입니다. 즉, 입력에 따라 같은 상태에서 다른 출력을 만들 수 있습니다.

> Mealy Machine은 State와 Input 까지 보기 때문에, 출력값에 Timing을 손해보게됩니다.(Delay)

특히 output이 나갈때, F/F을 거치지 않고 나간다면, Noise나 Glitch와 같은 오동작 원인이 유발할 수 있습니다.

Moore는 input을 안보기 때문에, 단방향으로 Data가 흘러가는 시스템에서 사용할 수 있습니다.

Ready/Valid 등 양방향 Handshake interface등을 사용하게 된다면 Mealy Machine을 이용하여 설계해야 합니다.

이처럼 설계의 경험치가 쌓이면서 각각의 장단을 고려해 설계해야 합니다.

실습) Core를 Control하기 위한 FSM설계

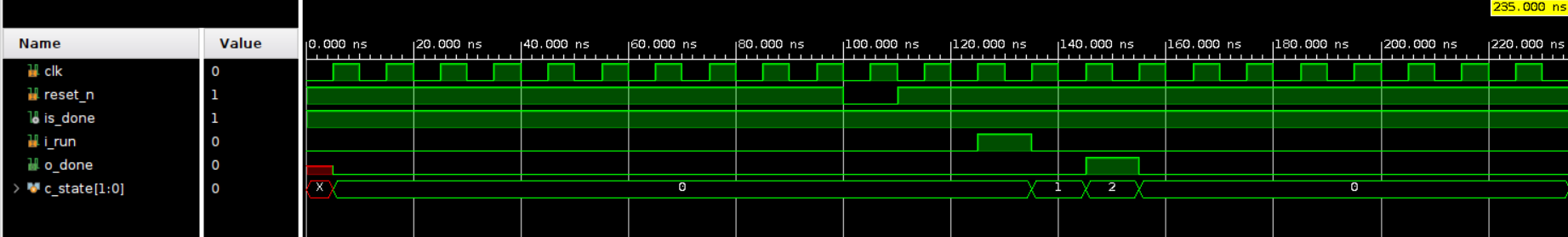

IDLE >> (i_run==1) >> RUN >> (is_done?) >> DONE >> IDLE

- 처음 Reset이 입력되면 IDLE상태가 됩니다. 그리고 i_run신호를 '1'로 Set하기 전까지 대기합니다.

- i_run신호가 '1'로 Set되면, IDLE에서 RUN으로 Transition이 발생합니다. is_done이 '1'이 될때 까지 유지합니다.

- is_done이 '1'이 되면 DONE 상태가 되고, 1Cycle뒤에 IDLE로 돌아옵니다.

- Verilog Code

* https://github.com/Vamosssss/Basic/tree/main/07.%20FSM/01.FSM%20Basic

'Verilog HDL > Basics' 카테고리의 다른 글

| 09-2. FSM(Finite State Machine) Typiclal Design (0) | 2024.10.07 |

|---|---|

| 09-1 . FSM(Finite State Machine) Coding Style (0) | 2024.10.07 |

| 08. Pipeline (1) | 2024.10.06 |

| 07. Counter (0) | 2024.10.06 |

| 06. Combination Logic (0) | 2024.10.06 |