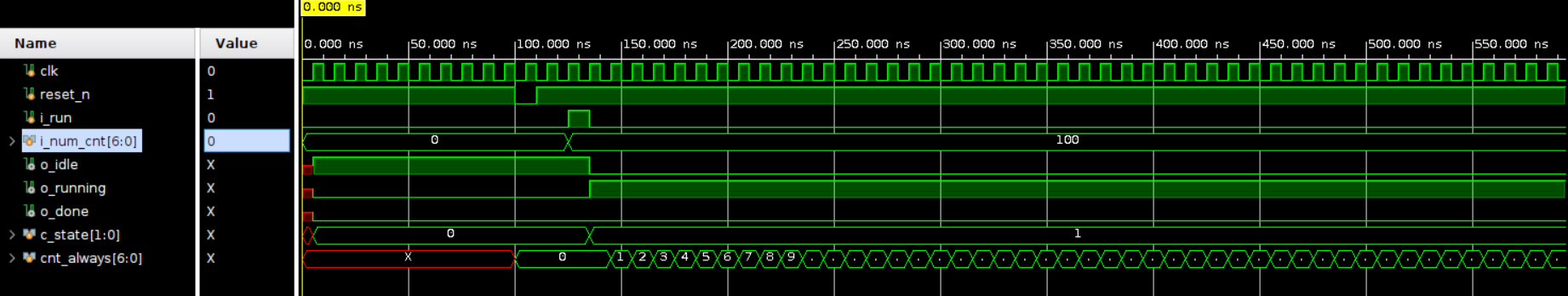

FSM + Counter

- Core가 IDLE인지 확인합니다.

- i_run신호와 counting 할 숫자를 core에 전달합니다.

- DONE이 될때까지 기다립니다.

- Verilog Code

* https://github.com/Vamosssss/Basic/tree/main/07.%20FSM/02.%20FSM%20%2B%20Counter

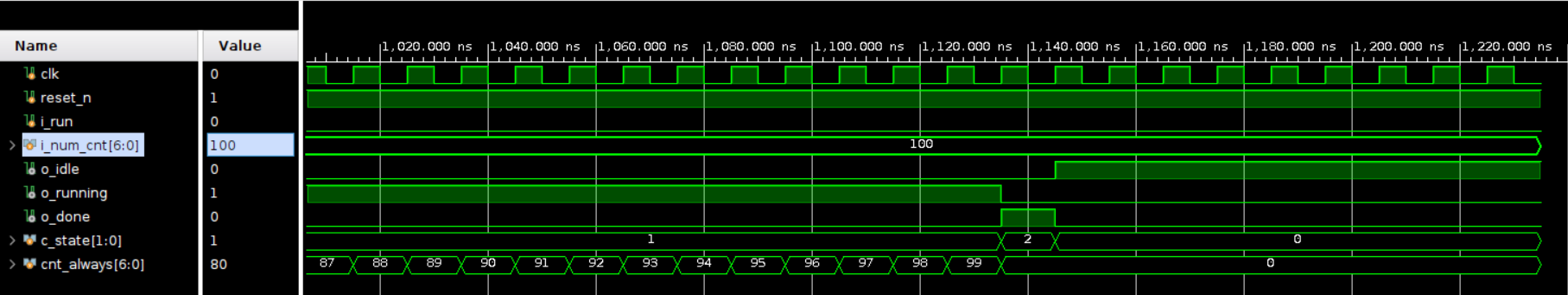

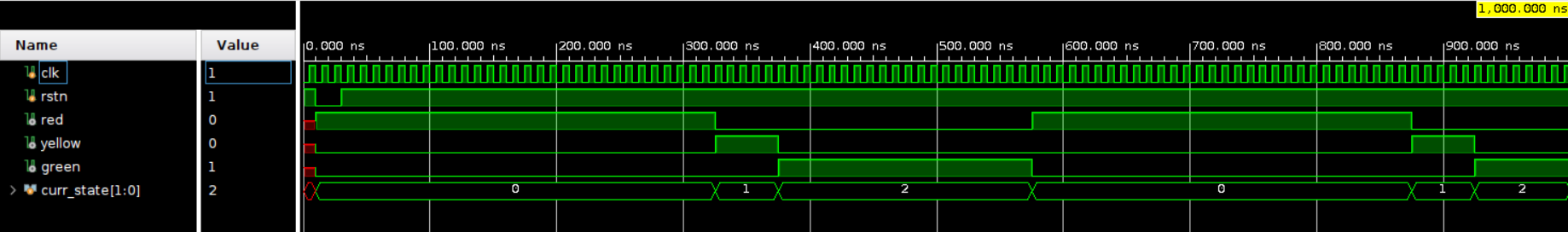

FSM(Traffic Light)

- RED will go to YELLOW after 30 cycles.

- YELLOW will go to GREEN after 5 cycles.

- GREEN will go RED after 20 cycles.

- The light color will be output.

- Verilog Code

* https://github.com/Vamosssss/Basic/tree/main/07.%20FSM/03.%20FSM(Traffic%20Light)

'Verilog HDL > Basics' 카테고리의 다른 글

| 11. Digital 설계에서 Memory (1) | 2024.10.08 |

|---|---|

| 09-4. FSM(Finite State Machine) 삼항연산자 (0) | 2024.10.08 |

| 09-3. FSM(Finite State Machine) Transition통합, 분리 (0) | 2024.10.07 |

| 09-2. FSM(Finite State Machine) Typiclal Design (0) | 2024.10.07 |

| 09-1 . FSM(Finite State Machine) Coding Style (0) | 2024.10.07 |