- CLK (Clock)

- CLK는 SRAM의 모든 동작을 동기화하는 클럭 신호입니다. 읽기 및 쓰기 연산은 클럭의 상승 또는 하강 에지에서 발생하며, 대부분의 동기식 SRAM은 클럭의 상승 에지에서 동작합니다.

- ADDR (Address)

- ADDR는 접근할 메모리 셀의 주소를 지정하는 신호입니다. 이 신호는 SRAM의 특정 위치에서 데이터를 읽거나 쓰기 위해 사용됩니다.

- DIN (Data Input)

- DIN은 쓰기 연산 시 입력되는 데이터 버스입니다. ADDR로 지정된 메모리 셀에 기록할 데이터를 담고 있습니다.

- DOUT (Data Output)

- DOUT은 읽기 연산 시 출력되는 데이터 버스입니다. ADDR로 지정된 메모리 셀에서 읽어온 데이터를 출력합니다.

- EN (Enable)

- EN은 SRAM을 활성화하는 신호입니다. EN이 활성화되면 SRAM이 동작할 준비가 되며, 비활성화 상태에서는 모든 동작이 중지되고 SRAM은 대기 상태에 들어갑니다. 읽기 및 쓰기 연산을 실행하려면 EN이 반드시 활성화되어야 합니다.

- WE (Write Enable)

- WE는 쓰기 연산을 제어하는 신호입니다. WE가 활성화되면 쓰기 모드로 동작하여 SRAM에 데이터를 기록할 수 있으며, WE가 비활성화된 경우 SRAM은 읽기 모드로 동작합니다.

Write Operation (쓰기 연산 과정)

- ADDR 설정: 쓰기할 메모리 위치를 선택하기 위해 ADDR 버스에 주소를 설정합니다.

- DIN 설정: 기록할 데이터를 DIN 버스에 입력합니다.

- EN 활성화: EN 신호를 활성화하여 SRAM을 동작 가능한 상태로 만듭니다.

- WE 활성화: WE 신호를 활성화하여 쓰기 모드를 설정합니다.

- CLK 상승 에지: 클럭 신호가 상승 에지에 도달하면, ADDR로 지정된 메모리 위치에 DIN 값이 기록됩니다.

- WE 비활성화: 쓰기 작업이 끝난 후 WE 신호를 비활성화하여 쓰기 작업을 종료합니다.

Read Operation (읽기 연산 과정)

- ADDR 설정: 읽고자 하는 메모리 위치를 선택하기 위해 ADDR 버스에 주소를 설정합니다.

- EN 활성화: EN 신호를 활성화하여 SRAM을 동작 가능한 상태로 만듭니다.

- WE 비활성화: WE 신호를 비활성화하여 읽기 모드로 전환합니다.

- CLK 상승 에지: 클럭 신호가 상승 에지에 도달하면, ADDR로 지정된 메모리 위치에서 데이터가 DOUT 버스를 통해 출력됩니다.

- DOUT 출력: ADDR에 저장된 데이터가 DOUT으로 읽혀집니다.

> Address0번지의 Data를 Read하고 싶을땐

en = 1, we = 0 >> Read Setting, Addr = 0 > dout에 Read Data가 올라옵니다.

> Address2번지에 Data를 Write하고 싶을땐

en = 1, we = 1 >> Write Setting, Addr = 2 >> din에 Write하고 싶은 data를 만들어줍니다.

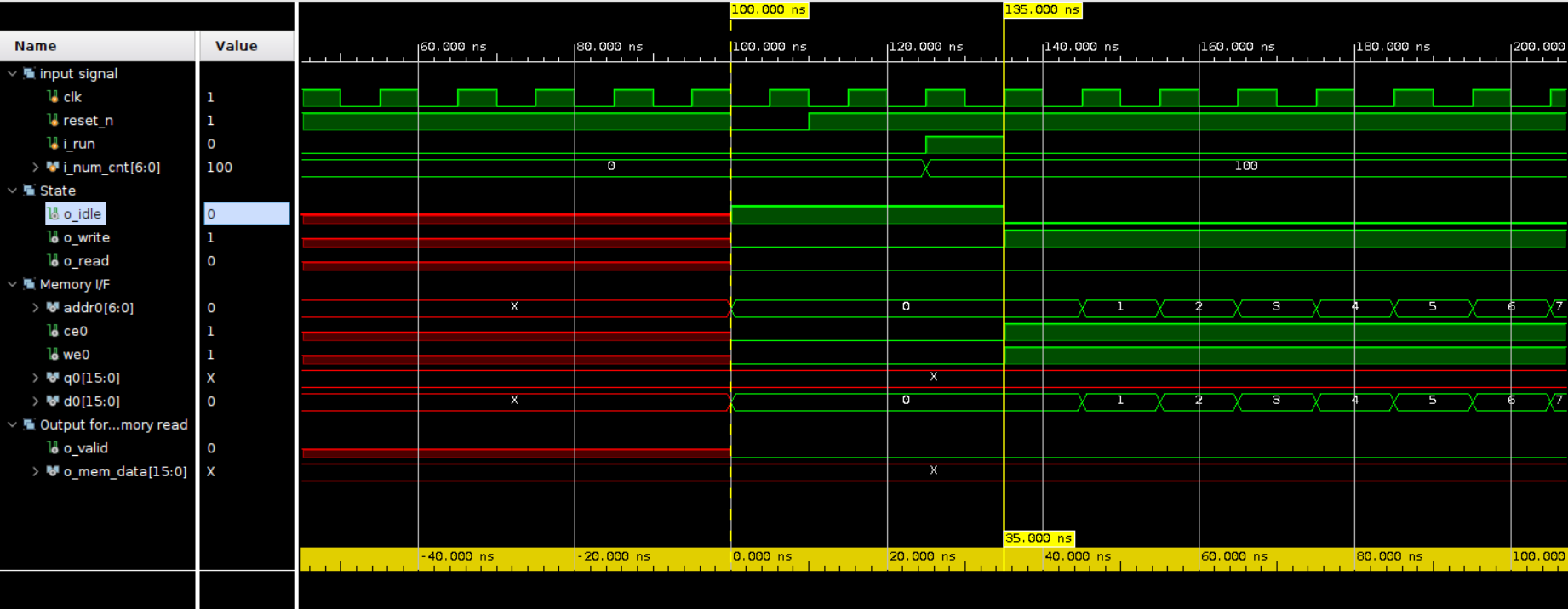

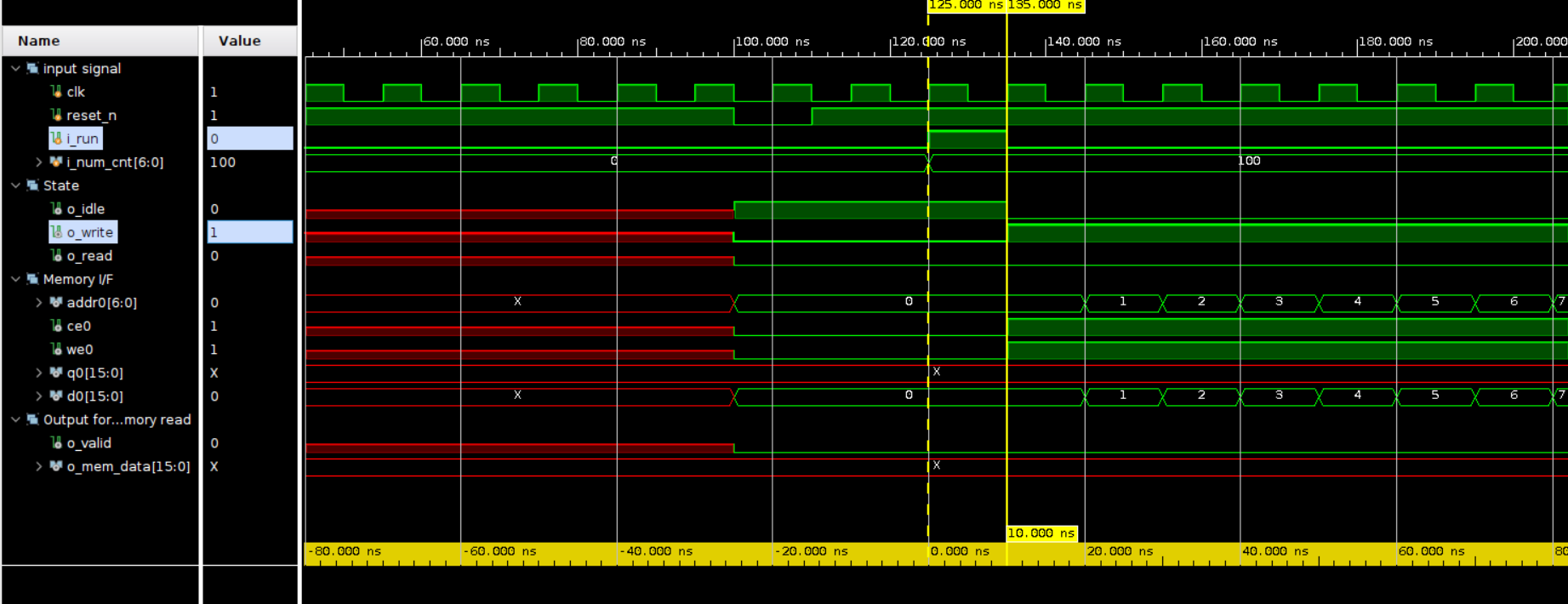

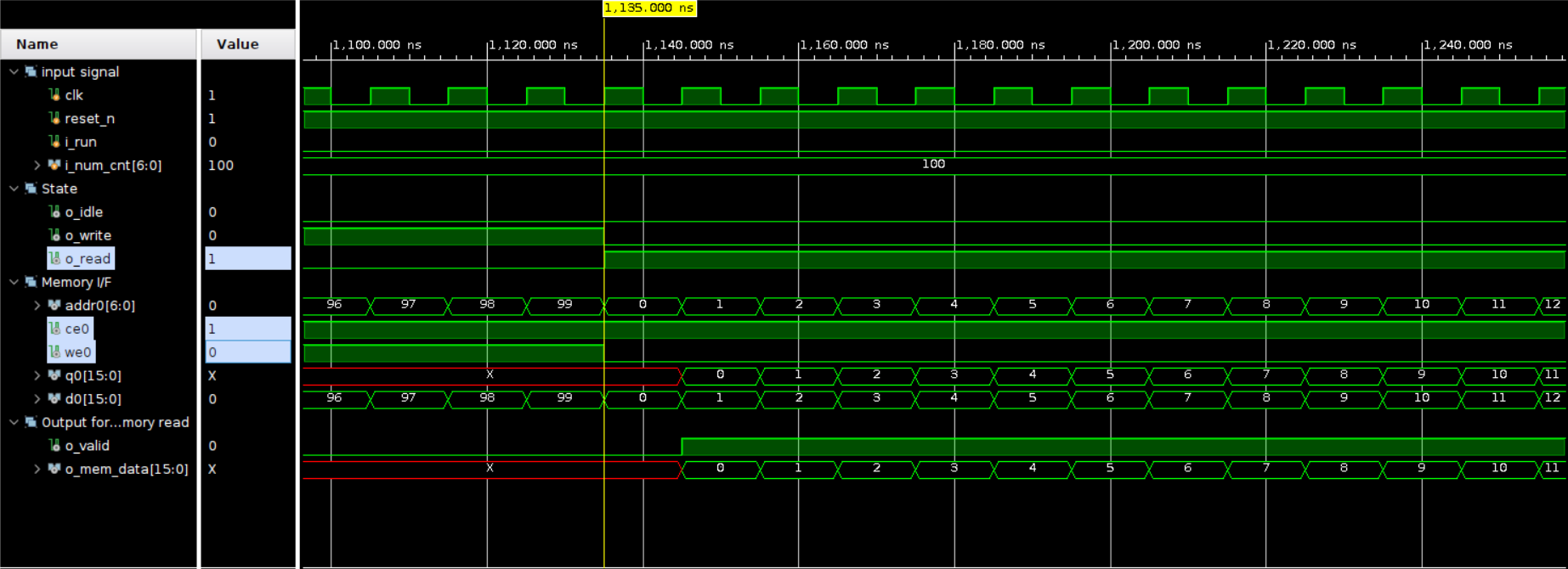

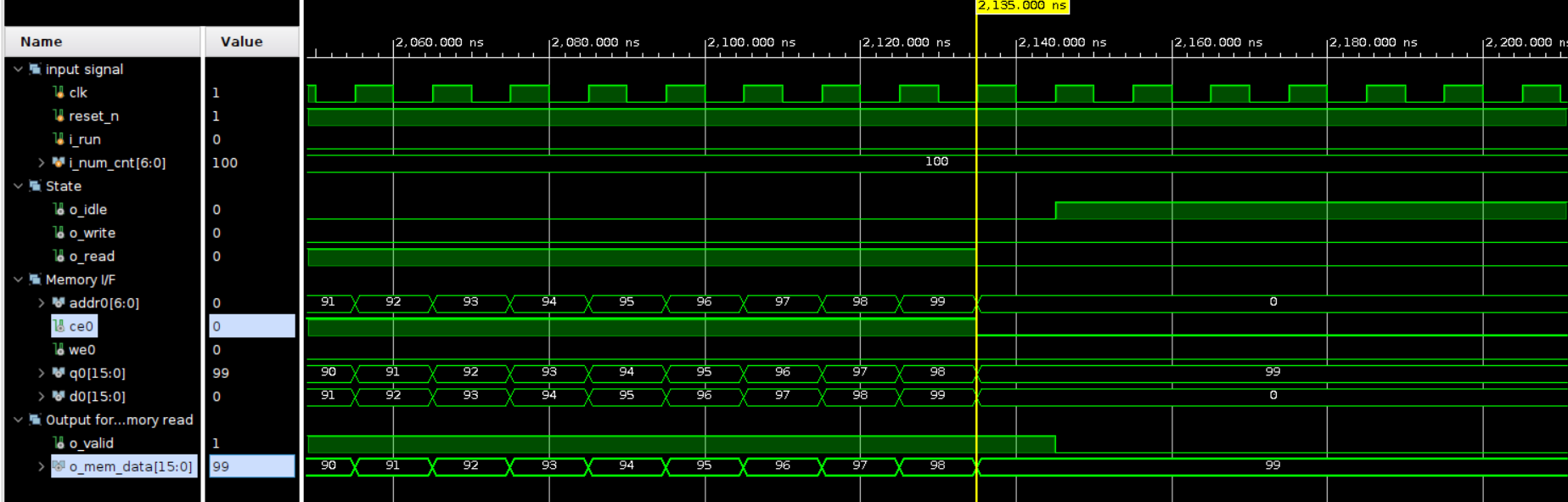

실습 ) BRAM에 Data를 Write/Read하기.

- IDLE상태를 확인하고, i_run신호와 num_cnt에 숫자를 입력합니다.

- 0~99까지의 Address에 data를 Write합니다.

- Address 0~99까지의 data를 Read합니다.

- Read가 끝난 후, DONE을 띄우고, 다시 IDLE로 돌아갑니다.

- Verilog Code

* https://github.com/Vamosssss/FPGA-Project/tree/main/01.%20BRAM%20Controller

'Verilog HDL > FPGA' 카테고리의 다른 글

| 03. FPGA(Field Programmable Gate Array) Usage (1) | 2024.10.09 |

|---|---|

| 01. FPGA의 BRAM이해하기(SRAM과 같은 동작 방식) (0) | 2024.10.08 |