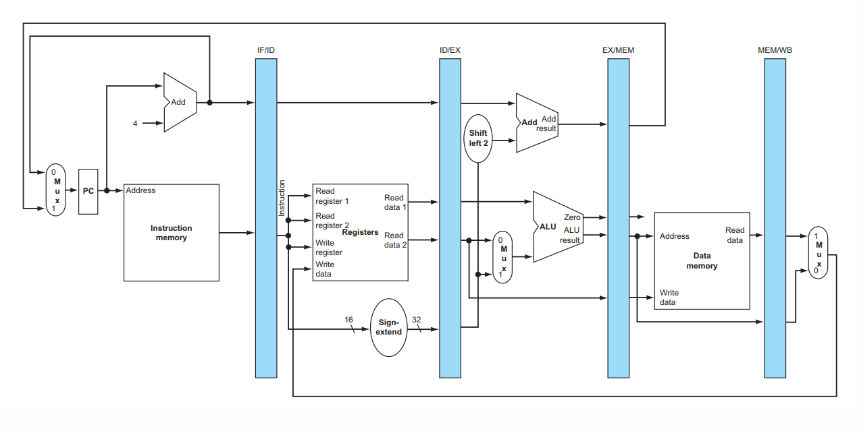

- 데이터 안정성: 파이프라인 레지스터는 각 단계에서 처리되는 데이터를 안정적으로 저장합니다. 이를 통해 다음 단계로 전달되는 데이터가 안정된 상태로 유지되므로, 데이터 무결성을 보장할 수 있습니다.

- 동기화: 각 단계는 클럭 주기에 따라 동작하며, 파이프라인 레지스터는 각 단계에서 처리된 결과를 동기화하는 역할을 합니다. 이는 CPU의 여러 구성 요소가 동일한 클럭 신호에 의해 제어되도록 하여 타이밍 문제를 방지합니다.

- 경합 방지: 파이프라인 구조에서는 여러 명령어가 동시에 처리되기 때문에 데이터 경합(race condition)이나 메타스테이빌리티(metastability) 문제를 일으킬 수 있습니다. 파이프라인 레지스터는 이러한 문제를 완화하고 안정적인 데이터 전달을 보장합니다.

- 병렬 처리 효율성: 파이프라인 레지스터는 명령어 간의 병렬 처리를 가능하게 합니다. 각 명령어가 다른 단계에서 동시에 처리되므로, CPU의 처리량(throughput)을 높이고 성능을 향상시킬 수 있습니다.

- 단계 간의 데이터 전송: 파이프라인 레지스터는 각 단계에서 처리된 데이터가 다음 단계로 원활하게 전달되도록 도와줍니다. 이를 통해 CPU가 여러 명령어를 동시에 처리할 수 있는 능력을 갖추게 됩니다.

- 설계의 유연성: 파이프라인 레지스터를 사용함으로써 설계자는 각 단계의 처리 시간을 조정하거나 추가적인 처리 단계를 삽입할 수 있는 유연성을 가질 수 있습니다. 이를 통해 성능 최적화 및 다양한 구조의 구현이 가능합니다.

- 복잡한 명령어 처리 지원: 파이프라인 레지스터는 복잡한 명령어 처리에 필요한 여러 단계를 효율적으로 관리할 수 있게 해줍니다. 각 단계에서 수행되는 작업이 많아질수록, 레지스터를 통해 작업을 분할하고 효과적으로 관리할 수 있습니다.

* https://hackmd.io/@yW7HKRexRASTmH3kBDXQpQ/Sy395BDg5#pipeline-overview

'CPU ARCHITECTURE1 > CPU' 카테고리의 다른 글

| 15. Hazard (0) | 2024.09.30 |

|---|---|

| 14. Active at same clock (0) | 2024.09.30 |

| 12. Advantage of Pipeline (0) | 2024.09.30 |

| 11. CPU DATA PATH - J - Type(JUMP) (0) | 2024.09.30 |

| 10. CPU DATA PATH - I -Type(Branch) (0) | 2024.09.30 |