1. 주소 페이즈 (Address Phase)

주소 페이즈는 마스터가 슬레이브로부터 데이터를 읽기 위해 요청하는 주소와 제어 신호를 설정하는 단계입니다. 이 단계에서 마스터는 슬레이브로부터 데이터를 읽기 위한 주소와 관련된 신호를 설정하여 전송합니다.

신호 설명:

- HADDR: 마스터가 슬레이브에서 읽고자 하는 주소를 나타냅니다.

- HTRANS: 전송 상태를 나타내는 신호로, IDLE, BUSY, NONSEQ, SEQ 등의 상태로 나뉩니다. 읽기 작업에서는 NONSEQ(비연속 전송) 또는 SEQ(연속 전송) 상태를 사용합니다.

- HWRITE: 읽기/쓰기 구분 신호로, 읽기 작업에서는 0으로 설정됩니다.

- HSIZE: 읽을 데이터의 크기를 나타내며, 8비트, 16비트, 32비트 등으로 설정됩니다.

- HBURST: 버스트 전송 유형을 나타냅니다. Single, Incrementing, Wrapping 등의 모드를 선택할 수 있습니다.

- HPROT: 보호 정보를 제공하며, 캐시 가능성, 버퍼링 가능성 등을 나타냅니다.

2. 데이터 페이즈 (Data Phase)

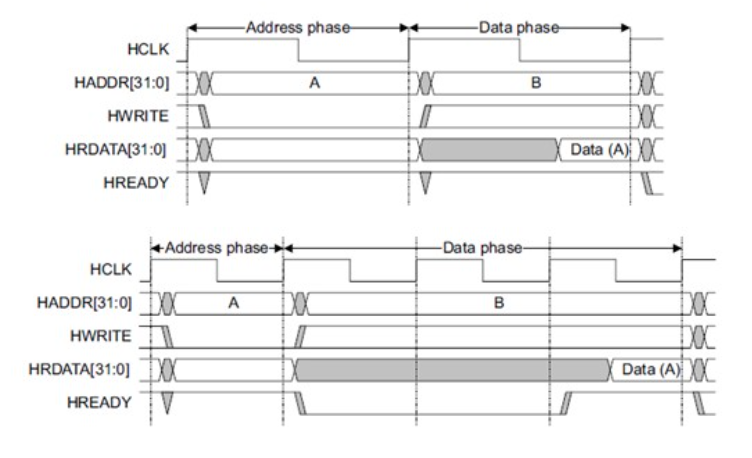

데이터 페이즈는 슬레이브가 마스터로 데이터를 반환하는 단계입니다. 데이터는 주소 페이즈 이후 한 클럭 사이클에서 슬레이브에 의해 마스터로 전송됩니다. 파이프라인 방식이므로 주소 페이즈와 데이터 페이즈가 겹쳐 진행될 수 있습니다.

신호 설명:

- HRDATA: 슬레이브가 마스터에게 전송하는 읽은 데이터입니다.

- HREADY: 슬레이브가 데이터를 준비했는지를 나타내며, HREADY가 LOW일 경우 마스터는 기다려야 합니다. HREADY가 HIGH일 경우 슬레이브는 데이터를 준비해 마스터로 보냅니다.

- HRESP: 슬레이브의 응답 상태를 나타내며, OKAY, ERROR, RETRY 등이 있습니다. OKAY는 성공적인 전송을, ERROR는 실패를 의미합니다.

3. 전송 완료

슬레이브가 데이터 전송을 완료하면, HREADY 신호를 HIGH로 설정하여 마스터에게 데이터를 읽을 준비가 완료되었음을 알립니다. 그 후 마스터는 HRDATA 포트로 슬레이브에서 전송된 데이터를 읽습니다. 만약 슬레이브가 데이터를 즉시 준비할 수 없다면, HREADY 신호를 LOW로 설정하여 마스터가 대기해야 하며, 슬레이브가 준비될 때까지 전송이 지연됩니다.

4. 파이프라인 구조

AHB는 파이프라인 구조로 동작하여, 주소와 데이터가 다른 클럭 사이클에 독립적으로 전송될 수 있습니다. 예를 들어, 첫 번째 클럭 사이클에서는 주소가 전송되고, 그 다음 클럭 사이클에서는 데이터가 준비되어 전송됩니다. 이렇게 하면 동시에 여러 전송 작업을 처리할 수 있어 버스 효율이 극대화됩니다.

AHB Read Operation 순서

- 마스터는 HADDR, HTRANS, HWRITE(0), HSIZE 등의 주소 및 제어 신호를 설정하여 슬레이브로 보냅니다.

- 슬레이브는 HREADY 신호를 통해 데이터를 준비 중임을 알립니다.

- 슬레이브가 데이터 준비를 완료하면, HREADY를 HIGH로 설정하고 HRDATA에 데이터를 출력하여 마스터에게 전송합니다.

- 슬레이브는 HRESP 신호로 전송 성공 여부를 알리며, OKAY 상태가 되면 전송이 성공적으로 완료됩니다.

- 마스터는 데이터를 수신한 후, 다음 전송 작업을 진행할 수 있습니다.

AHB Read Operation의 주요 특징

- 파이프라인 방식: 주소와 데이터가 서로 다른 클럭 사이클에서 전송되므로, 여러 작업을 동시에 진행할 수 있어 성능을 높입니다.

- 버스트 전송 지원: AHB는 연속된 메모리 주소에 대해 여러 데이터를 읽어오는 버스트 전송을 지원합니다. 이는 대용량 데이터를 효율적으로 처리하는 데 유용합니다.

- HREADY 신호: 슬레이브가 데이터를 준비하지 못한 경우, HREADY 신호를 LOW로 설정하여 마스터가 대기하도록 합니다. 마스터는 HREADY가 HIGH로 설정될 때까지 기다려야 합니다.

파이프라인 동작 예시

- Cycle 1: 마스터가 슬레이브로 읽기 작업을 요청하며, 주소를 HADDR에 전송.

- Cycle 2: 슬레이브가 데이터를 준비 중이며, HREADY는 LOW. 마스터는 대기.

- Cycle 3: 슬레이브가 HRDATA에 데이터를 준비하고, HREADY는 HIGH. 마스터는 데이터를 읽음.

- Cycle 4: 마스터는 새로운 읽기 작업을 시작할 수 있음.

'SoC Protocol > AMBA' 카테고리의 다른 글

| 09. AXI Channel (0) | 2024.09.27 |

|---|---|

| 08. AHB (HTRANS, HSIZE, HBURST) (0) | 2024.09.27 |

| 06. AHB Write Operation (0) | 2024.09.27 |

| 05. AHB Interface (0) | 2024.09.27 |

| 04. APB Read Transfer (0) | 2024.09.27 |