Instruction fetch는 CPU가 프로그램의 명령어를 메모리에서 읽어오는 과정으로, 명령어 사이클의 첫 번째 단계입니다. 이 과정에서 CPU는 명령어를 가져와 실행 준비를 합니다. 주요 단계는 다음과 같습니다:

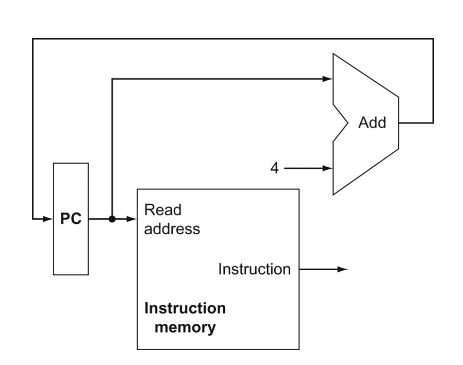

- Program Counter (PC) 확인:

CPU는 현재 실행할 명령어의 주소를 저장하는 **프로그램 카운터(PC)**를 참조합니다. PC는 다음 명령어의 주소를 가리키고 있습니다. - 명령어 메모리 접근:

CPU는 메모리에서 PC가 가리키는 주소에 있는 명령어를 읽습니다. 이 메모리는 일반적으로 명령어 캐시나 **메인 메모리(RAM)**가 될 수 있습니다. 명령어 캐시는 메모리보다 접근 속도가 빠르므로, 캐시에 명령어가 있을 경우 CPU는 더 빠르게 명령어를 가져올 수 있습니다. - 명령어 가져오기:

CPU는 PC가 가리키는 메모리 위치로부터 명령어를 읽어 **명령어 레지스터(IR)**에 저장합니다. 이때, 명령어는 일반적으로 고정된 길이(예: 32비트)의 이진 코드로 구성됩니다. - Program Counter 증가:

CPU는 다음 명령어를 가리키도록 PC를 증가(Increment) 시킵니다. 대부분의 CPU에서 명령어 길이는 고정되어 있기 때문에 PC는 일정한 크기(예: 4바이트)만큼 증가합니다. - 명령어 디코딩 준비:

명령어를 가져온 후, CPU는 해당 명령어를 해석하기 위한 디코딩 단계로 넘어가게 됩니다. 디코딩 과정에서는 명령어의 형식을 해석하고, 수행할 연산을 결정합니다.

Instruction Fetch 과정은 CPU의 파이프라인 구조에서도 중요한 역할을 합니다. 파이프라인 CPU에서는 여러 명령어가 동시에 처리되므로, 명령어를 효율적으로 가져오는 것이 중요합니다.

이 과정에서 발생할 수 있는 주요 문제로는 캐시 미스, 파이프라인 버블 및 분기 예측 실패 등이 있습니다. 예를 들어, 분기 예측이 실패하면 잘못된 명령어를 가져오게 되어 성능 저하가 발생할 수 있습니다.

* https://cs.middlesexcc.edu/~schatz/csc264/handouts/mips.datapath.html

'CPU ARCHITECTURE1 > CPU' 카테고리의 다른 글

| 05-3. Execute(EX) (0) | 2024.09.30 |

|---|---|

| 05-2. Instruction Decode (ID) (0) | 2024.09.30 |

| 05. CPU 5-Stage Pipeline (0) | 2024.09.30 |

| 04. SPR(Special Purpose Register) (0) | 2024.09.29 |

| 03. CPU main components (1) | 2024.09.29 |